编辑内容

| Features | Capability | Description | Patterns |

|---|---|---|---|

| Layer count | 1-32 Layers | The number of copper layers in the PCB | |

| Controlled Impedance | 4/6/8/10/12/14/16/18/20/.../32 layers |

User Guide to the EAZYPCB Impedance Calculator EAZYPCB Impedance Calculator |

|

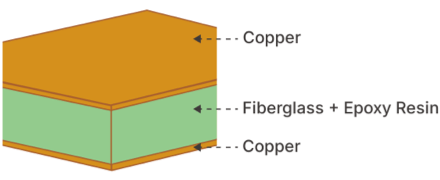

| Material | FR-4 | Grade A laminates from suppliers including Nan Ya, KB, Shengyi and etc. |  |

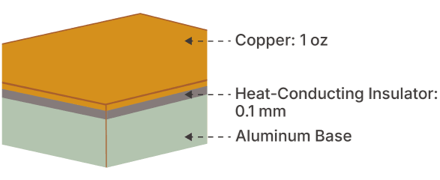

| Aluminum-Core | 1-layer Aluminum-core PCBs |  |

|

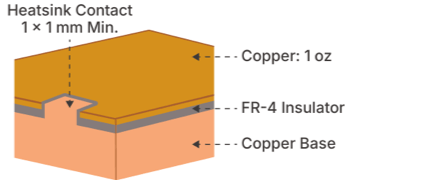

| Copper-Core | 1-layer copper-core PCBs with direct heatsink contacts (≥ 1 × 1 mm) |  |

|

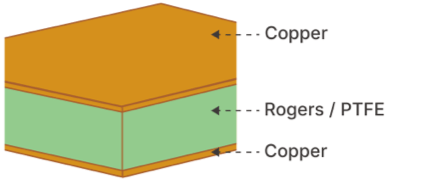

| RF PCB | 1 oz copper, 2-layer RF PCBs with Rogers and PTFE cores |  |

|

| FR-4 Dielectric Constants | 4.5 (2-Layer PCB) |

7628 Prepreg 4.4 3313 Prepreg 4.1 2116 Prepreg 4.16 |

|

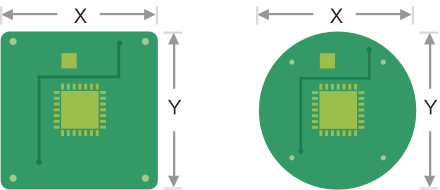

| Maximum Dimensions |

FR4 PCB: 670 × 600 mm Rogers / PTFE Teflon PCB: 590 × 438 mm Aluminum PCB: 602 × 506 mm Copper PCB: 480 × 286 mm |

These limits apply to PCBs with thickness ≥ 0.8 mm. The thinner FR4 PCBs are 500 × 600 mm maximum. 2-layer FR4 PCBs can reach a maximum size of 1020 × 600 mm. |

|

| Minimum Dimensions | Regular: 3 × 3 mm. Castellated / Plated Edges: 10 × 10 mm. | These limits apply to PCBs with thickness ≥ 0.6 mm. Manual review required for thinner PCBs. Panelization is recommended for small-sized boards. | |

| Dimension Tolerance | ±0.1mm | ±0.1mm(Precision) and ±0.2mm(Regular) for CNC routing, and ±0.4mm for V-scoring | |

| Thickness | 0.4 - 4.5 mm | Thickness for FR4 are: 0.4/0.6/0.8/1.0/1.2/1.6/2.0 mm (2.5 mm and above are for 12+ layer PCBs only) |  |

| Thickness Tolerance (Thickness≥1.0mm) | ± 10% | e.g. For the 1.6mm board thickness, the finished board thickness ranges from 1.44mm(T-1.6×10%) to 1.76mm(T+1.6×10%) | |

| Thickness Tolerance (Thickness<1.0mm) | ± 0.1mm | e.g. For the 0.8mm board thickness, the finished board thickness ranges from 0.7mm(T-0.1) to 0.9mm(T+0.1). | |

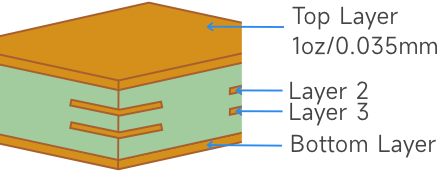

| Finished Outer Layer Copper | 1 oz / 2 oz (35um / 70um) | Finished copper weight of outer layer is 1oz or 2oz. |  |

| Finished Inner Layer Copper | 0.5 oz / 1 oz / 2 oz (17.5um / 35um / 70um) | Finished copper weight of inner layer is 0.5oz by default. |  |

| Soldermask | Green, Purple, Red, Yellow, Blue, White, and Black. | We use LPI (Liquid Photo Imageable) solder mask. This is the most common type of mask used today. Heat-cured ink soldermask is usually found on low-cost, single-sided PCBs. | |

| Surface Finish | HASL (leaded /lead-free), ENIG, OSP (copper core boards only) | FR4 has all three finishes available, 6+ layers and RF boards only have ENIG. Aluminum core boards only have HASL. Copper core boards only have OSP. |

编辑内容

| Features | Capability | Description | Patterns |

|---|---|---|---|

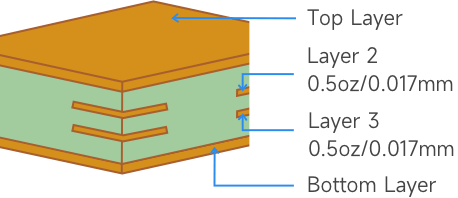

| Drill Diameter |

1-layer: 0.3 – 6.3 mm

2-layer: 0.15 – 6.3 mm Multilayer: 0.15 – 6.3 mm |

Holes with diameter ≥ 6.3 mm are CNC routed from a smaller drilled hole.

Min. drill diameter for 2- or more-layer PCBs is 0.15 mm (more costly) Min. drill diameter for aluminum-core PCBs is 0.65 mm Min. drill diameter for copper-core PCBs is 1.0 mm |

|

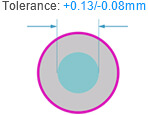

| Hole size Tolerance (Plated) |

Through-holes: +0.13 / -0.08 mm

Press-fit holes: ±0.05 mm (multilayer EMI boards only – mention the specific holes in PCB Remark) |

e.g. for the 0.6mm hole size, the finished hole size between 0.52mm to 0.73mm is acceptable.

|

|

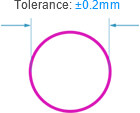

| Hole size Tolerance (Non-Plated) |

±0.2mm

|

e.g. for the 1.00mm Non-Plated hole, the finished hole size between 0.80mm to 1.20mm is acceptable.

|

|

| Average Hole Plating Thickness |

18μm

|

||

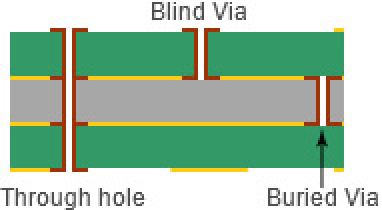

| Blind/Buried Vias |

Not supported

|

Currently we don't support Blind/Buried Vias, only make through holes.

|

|

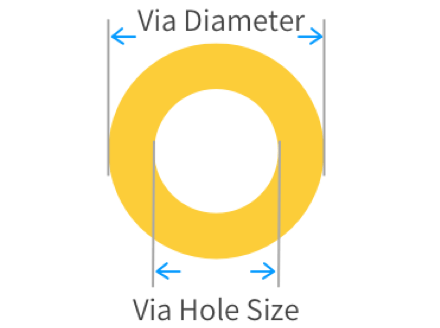

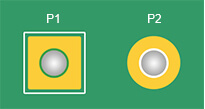

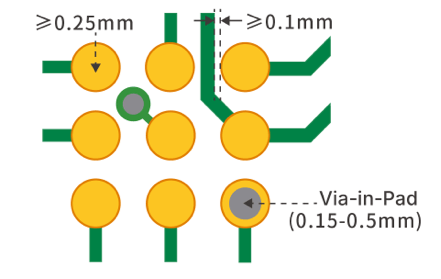

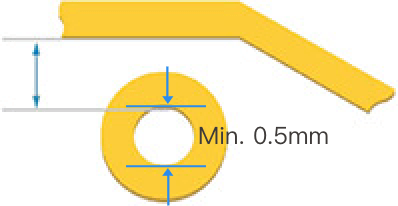

| Min. Via hole size/diameter |

0.15mm / 0.25mm

|

1-layer (NPTH only): 0.3 mm hole size / 0.5 mm via diameter

2-layer: 0.15mm hole size / 0.25mm via diameter Multilayer: 0.15 mm hole size / 0.25 mm via diameter ① Via diameter should be 0.1mm(0.15mm preferred) larger than Via hole size. ② Preferred Min. Via hole size: 0.2mm |

|

| Min. Non-plated holes |

0.50mm

|

Please draw NPTHs in the mechanical layer or keep out layer.

|

|

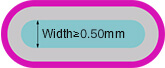

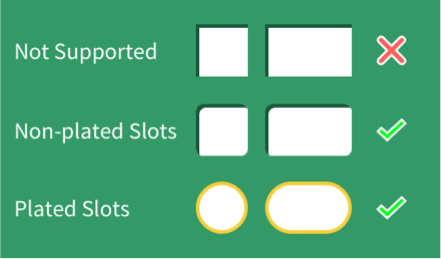

| Min. Plated Slots |

0.5mm

|

The minimum plated slot width is 0.5mm, which is drawn with a pad.

|

|

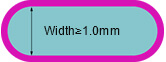

| Min. Non-Plated Slots |

1.0mm

|

The minimum Non-Plated Slot Width is 1.0mm, please draw the slot outline in the mechanical layer(GM1 or GKO)

|

|

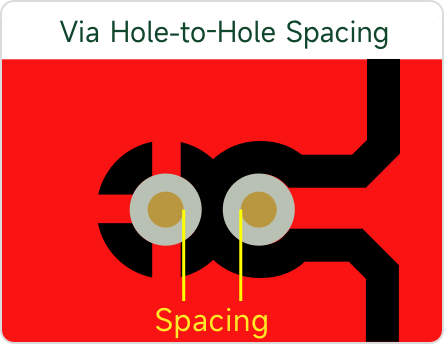

| Via Hole-to-Hole Spacing |

0.2mm

|

|

|

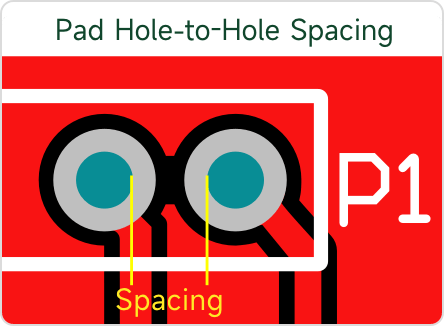

| Pad Hole-to-Hole Spacing |

0.45mm

|

|

|

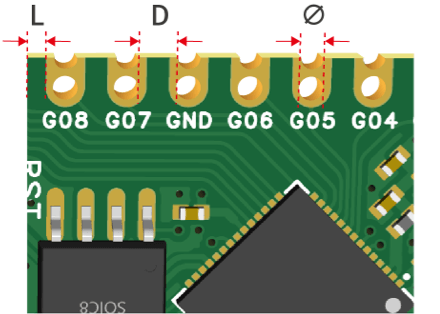

| Min. Castellated Holes |

0.60mm

|

Castellated holes are metalized half-holes on PCB edges, commonly used on daughter boards to be soldered onto carrier PCBs.

① Hole diameter (Ø): ≥ 0.6 mm ② Hole to board edge (L): ≥ 1 mm ③ Hole to hole (D): ≥ 0.6 mm ④ Min. PCB size: 10 × 10 mm ⑤ Min. PCB thickness: 0.6 mm |

|

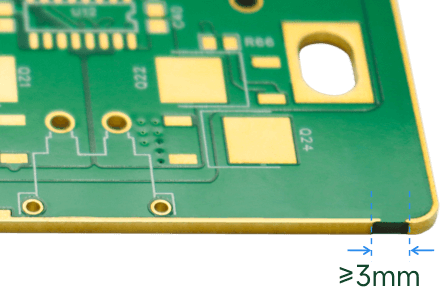

| Plated Edges |

10 x 10mm

|

Plated edges are copper-plated and ENIG treated, HASL is not supported.

① Min. PCB size: 10 × 10 mm ② Min. PCB thickness: 0.6 mm ③ At least 3 breaks (more for larger PCBs) in the edge plating are required for support tab connections |

|

| Rectangular Holes / Slots |

Not supported

|

Rectangular holes and slots without rounded corners are not supported.

|

|

编辑内容

| Features | Capability | Description | Patterns |

|---|---|---|---|

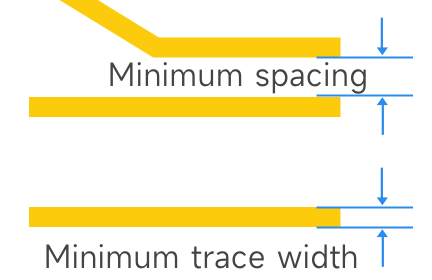

| Min. track width and spacing (1 oz) |

0.10 / 0.10 mm (4 / 4 mil)

|

1- and 2-layer: 0.10 / 0.10 mm (4 / 4 mil)

Multilayer: 0.09 / 0.09 mm (3.5 / 3.5 mil), 3 mil is acceptable in BGA fan-outs. |

|

| Min. track width and spacing (2 oz) |

0.16 / 0.16 mm (6.5 / 6.5 mil)

|

2-layer: 0.16 / 0.16 mm (6.5 / 6.5 mil)

Multilayer: 0.16 / 0.20 mm (6.5 / 8 mil) |

|

| Track width tolerance |

±20%

|

e.g. For a 0.1 mm track, the finished track width ranges from 0.08 and 0.12 mm.

|

|

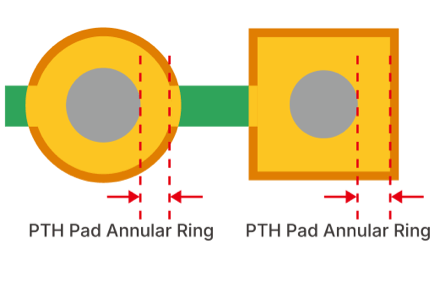

| PTH annular ring |

≥0.20mm

|

2-layer:

1 oz: Recommended 0.25 mm or above; absolute minimum 0.18 mm 2 oz: 0.254 mm or above Multilayer: 1 oz: Recommended 0.20 mm or above; absolute minimum 0.15 mm 2 oz: 0.254 mm or above |

|

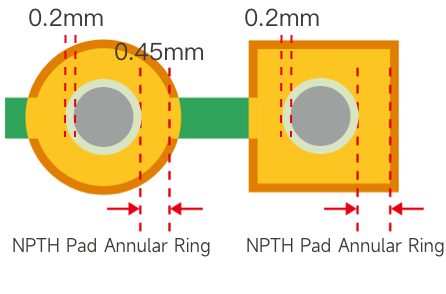

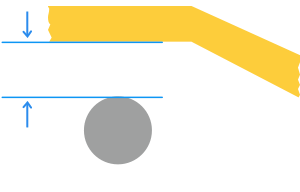

| NPTH pad annular ring |

≥0.45mm

|

Recommended 0.45 mm or more. This is to allow a 0.2 mm ring of copper to be removed around the hole for the sealing film to attach. Pad sizes smaller than the recommended value can result in the annular ring being very thin or completely missing.

|

|

| BGA |

0.25mm

|

① BGA pad diameter ≥ 0.25 mm

② BGA pad to trace clearance ≥ 0.1 mm (min. 0.09 mm for multilayer boards) ③ Vias can be placed within BGA pads using filled and plated-over vias |

|

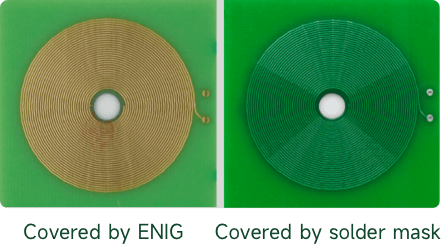

| Trace coils |

0.15/0.15mm

|

Minimum trace width/clearance: 0.15/0.15mm, when traces are covered by solder mask (1oz)

Minimum trace width/clearance: 0.25/0.25mm, when traces are NOT covered by solder mask (1oz). ENIG only(high risk of short circuit with HASL) |

|

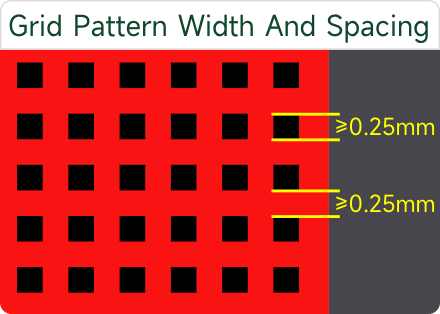

| Hatched grid width and spacing |

0.25 mm

|

|

|

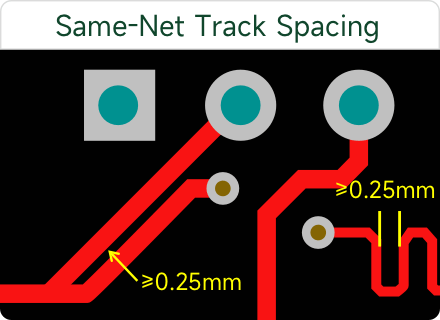

| Same-net track spacing |

0.25mm

|

|

|

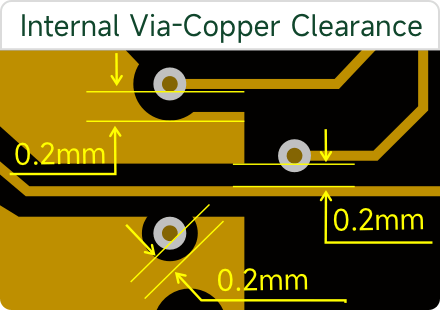

| Inner layer via hole to copper clearance |

0.2mm

|

|

|

| Inner layer PTH pad hole to copper clearance |

0.3mm

|

||

| Pad to track clearance |

0.1mm

|

Min. 0.1 mm (stay well above if possible). Min. 0.09 mm locally for BGA pads

|

|

| SMD pad to pad clearance (different nets) |

0.15mm

|

More details of SMD pad spacing: SMD Components Minimum Spacing

|

|

| Via hole to Track |

0.2mm

|

|

|

| PTH to Track |

0.25mm

|

0.35mm is recommended, minimum 0.25mm

|

|

| NPTH to Track |

0.2mm

|

|